当前位置:首页 > FPGA原型验证平台

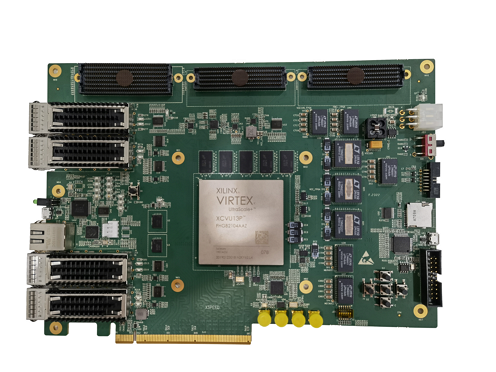

VU13P验证板卡

· FPGA:Virtex UltraScale+ XCVU13P-2FHGB2104I;

· DDR4 :1组DDR4 Compoents 80 bit;

· PCIe总线,Gen3,x16;

· 4个QSFP28光模块接口,速率4x25G,支持CMAC;

· 支持1路SGMII千兆以太网(88E111还是88E1512还没定);

· 支持2个FMC HPC(VITA 57.1 FMC HPC),两个HPC都要接GTY,暂定每个HPC 接8个GTY;

· 支持1个FMC+ (VITA 57.4 FMC+ Interface);

· 支持1路miniUSB串口,FT4232HL_LQFP64可以产生串口;

· 支持1路SD卡

· 两片1Gb FPGA配置FLASH,型号为MT25QU01GBBB8E12-0AAT,BGA封装

· User I/O (4-pole DIP switch, 6 each push-button switches, 8 x LED),参考VCU118

· 2x SMA MGT Reference Clock inputs,参考VCU118

· 1 SMA User Clock input,,参考VCU118

· 支持JTAG在线调试接口,电路上两种兼容设计,一种是我们原来的,还有一种是FT4232HL_LQFP64芯片实现,有参考原理图;

· 板卡供电为PCIe槽供电+外部供电;

· 前面板FPGA状态指示灯,板内调试指示灯;

· I2C,可根据管脚数量情况,参考VCU118;

· ZL30265产生多路时钟芯片用来替换原来VU9P验证板上的晶振,实现频率可动态配置,替换9P验证板原理图上的U30、U49、U53、U54。

· QSFP的参考时钟采用晶振+时钟缓冲器的方式,每个QUAD的两路参考时钟频率分别为125M和156.25M,其中156.25M采用晶振产生,125M用ZL30265产生,时钟缓冲器型号为SY89833ALMG。